РАЗРАБОТКА ЗАКОНЧЕННОГО МОДУЛЯ ВОСЬМИРАЗРЯДНОГО СУММАТОРА ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ

Конференция: LXXIX Международная научно-практическая конференция «Научный форум: инновационная наука»

Секция: Технические науки

LXXIX Международная научно-практическая конференция «Научный форум: инновационная наука»

РАЗРАБОТКА ЗАКОНЧЕННОГО МОДУЛЯ ВОСЬМИРАЗРЯДНОГО СУММАТОРА ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ

DEVELOPMENT OF A COMPLETE MODULE OF AN EIGHT-BIT SEQUENTIAL ADDER

Artem Gudzenko

Bachelor of Technical Sciences, Bauman Moscow State Technical University. N.E. Bauman, Russia, Moscow

Nikita Beletsky

Bachelor of Technical Sciences, Moscow Aviation Institute (National Research University), Russia, Moscow

Аннотация. Объектом разработки является модуль восьмиразрядного сумматора последовательного действия.

Цель работы – создание полного комплекта конструкторской документации для модуля восьмиразрядного сумматора последовательного действия.

При проектировании решены следующие задачи: анализ объекта разработки на функциональном уровне, разработка функциональной схемы модуля, выбор элементной базы для реализации объекта, разработка принципиальной схемы модуля, расчет электрических параметров.

Результатом проектирования является комплект конструкторской документации для изготовления устройства.

Abstract. The object of development is a module of an eight-bit adder sequential action.

The purpose of the work is to create a set of design documentation for a complete module of an eight-bit adder of sequential action.

When designing, the following tasks were solved: analysis of the development object at the functional level, development of the functional diagram of the module, selection of the element base for the implementation of the object, development of the circuit diagram of the module, calculation of electrical parameters.

The design result is a set of design documentation for the manufacture of the device.

Ключевые слова: СУММАТОР, ТТЛ, ТТЛШ, СХЕМА.

Keywords: SUMMATOR, TTL, LSTTL, DIAGRAM.

ПЕРЕЧЕНЬ СОКРАЩЕНИЙ И ОБОЗНАЧЕНИЙ

В настоящем документе применены следующие сокращения и обозначения:

ЛЭ – логический элемент

МС – микросхема

ТТЛ – Транзисторно-транзисторная логика;

ТТЛШ – Транзисторно-транзисторная логика Шоттки;

ШД – шина данных

ВВЕДЕНИЕ

В данной работе производится разработка законченного модуля восьмиразрядного сумматора последовательного действия.

Модуль восьмиразрядного сумматора последовательного действия предназначен для проведения операции сложения двух чисел.

Актуальность разрабатываемого устройства в сфере современной вычислительной технике объясняется следующим: сложение занимает доминирующее место среди арифметических операций. Обработка сигналов, функционирование цифровых фильтров, решение задач наведения и робототехники, мониторинга различных процессов, статистическая обработка, маршрутизация информационных потоков и т.д. требуют применения высокопроизводительных цифровых и символьных средств обработки информации. Очевидно, что повышение скорости выполнения операции сложения дает возможность ускорить все другие арифметические операции.

ОСНОВНАЯ ЧАСТЬ

1 Анализ требований

Основной задачей работы устройства является формирование результирующего восьмибитного слова путем последовательного потактного сложения заданных параметров, которыми являются два восьмибитных слова, а также начальный бит переноса.

1.1 Принцип работы разрабатываемого устройства

Два начальных числа подаются на схему через шину данных (ШД) и записываются в два восьмибитных регистра сдвига. ШД устройства шестнадцатибитная, бит переноса подается на устройство отдельным сигналом.

После записи чисел, регистры сдвига каждый так будут выдавать по одному биту на выход, начиная с младшего разряда, тем самым параллельный код преобразуется в последовательный.

Данные с выходов регистров подаются на одноразрядный сумматор, который высчитывает результат сложения, а также бит переноса. Бит переноса будет подаваться на вход одноразрядного сумматора на следующий такт. При сложении самых младших битов будет использоваться бит переноса, поданный на схему вместе с начальными значениями чисел. За выбор нужного бита переноса отвечает мультиплексор, который буде выдавать на 1 такте – бит заданный, как начальное значение, на всех остальных тактах – бит переноса, посчитанный при сложении предыдущих разрядов. Для правильной выборки используется счетчик и комбинация логических элементов, которые будут формировать бит выбора для мультиплексора. Выходные значения записываются в сдвиговый регистр, результирующий бит переноса будет выводиться отдельным сигналом.

1.2 Выбор схемотехнического решения

Первоочередной задачей является запись данных в регистры, для хранения данных будет использоваться следующее решение:

- Два сдвиговых регистра, преобразующих параллельный код в последовательный.

Далее необходимо реализовать одноразрядный сумматор. Для этого используются следующие элементы:

- Два элемента «Исключающее ИЛИ». Первый элемент определяет результат сложения двух битов чисел, а второй – «прибавляет» к результату, полученному на первом элементе, бит переноса.

- Два элемента «И». Данные элементы необходимы для определения переполнения при сложении битов. Один элемент определяет, было ли переполнение, принимая на вход биты чисел, и, соответственно, выдаст «1», если биты обоих чисел равны «1». Второй элемент отслеживает переполнение при сложении суммы двух изначально поданных битов и бита переполнения.

- Элемент «ИЛИ». Данный элемент принимает на вход значения с элементов «И», тем самым рассматривая все возможные варианты переполнения.

Далее необходимо, чтобы бит переноса подавался на вход одноразрядного сумматора на следующий такт. Для этого используется D-триггер, который будет обеспечивать необходимую задержку.

Необходимо также предусмотреть наличие элемента, который будет отвечать за подсчет тактов работы схемы, чтобы правильно выдавать управляющие сигналы на различные элементы схемы. Будем использовать:

- Четырехбитный программируемый счетчик.

- Элемент «4 ИЛИ-НЕ». Данный элемент позволит определить является ли текущий такт 1 или нет. Для этого на вход будут подаваться 4 бита со счетчика. Результат данного элемента будет являть управляющим сигналом для выбора бита переноса.

За выбор нужного бита переноса будет отвечать:

- Мультиплексор. Данный элемент позволит выбирать на каждом такте правильный бит переноса. Для этого в качестве управляющего сигнала будет подаваться результат с элемента «4 ИЛИ-НЕ».

Выходное значение и результирующий бит переноса должны также храниться в регистре. Это реализовано с помощью:

- Двух сдвиговых регистров, преобразующих последовательный код в параллельный.

2. Синтез функциональной схемы

На основании выбранного схемотехнического решения были выделены функции устройства и реализующие их блоки – блок приема, блок промежуточного подсчета, блок выборки, блок выдачи ответа. Опишем подробнее каждый функциональный блок и рассмотрим их взаимодействие.

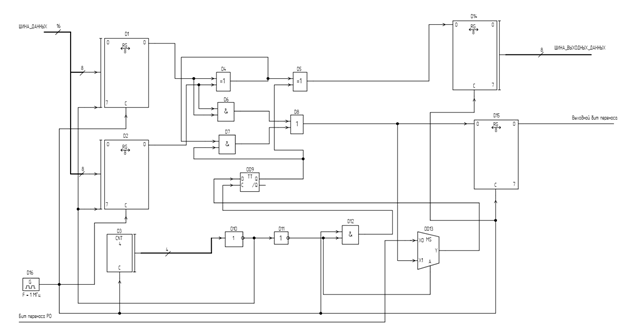

Разработанная функциональная схема восьмиразрядного сумматора последовательного действия представлена на рисунке 1 и также содержится в приложении Б.

Рисунок 1. Функциональная схема устройства

2.1 Блок выборки

Основа блока выборки – четырехразрядный счетчик. Счетчик обеспечивает подсчет тактов. На основе счетчика будут формироваться управляющий сигнал для мультиплексора, выбирающего биты переноса, а так же бит управления для выходных регистров.

На выходе счетчика стоит элемент «4 ИЛИ-НЕ». Данный элемент будет определять идет 1 такт работы или нет. Далее этот сигнал будет подаваться на мультиплексор, который будет определять, какой бит переноса выбрать. На вход мультиплексора подаются два бита: бит переноса для 1 такта работы сумматора, который задается пользователем, и бит переноса для всех остальных тактов работы схемы, посчитанный на предыдущем такте работы одноразрядного сумматора.

Бит управления для выходных регистров – это бит, который после окончания работы схемы, запретит выходным регистрам записывать новые значения. Данный сигнал формируется с помощью ряда логических элементов, благодаря которым можно сформировать сигнал, который запретит работу выходных регистров. Сигнал поступает на D-триггер как тактовый сигнал, а в качестве данных на вход подается запрещающий сигнал, который поступит на выходные регистры исключительно после определенного такта, который будет означать конец работы схемы.

2.2 Блок приема

Функциональный блок приема данных состоит из двух сдвиговых регистров, в которых и будут записаны начальные значения. Запись данных будет производиться по разрешающему сигналу. Разрешающий сигнал будет подаваться от блока выборки.

Далее, каждый такт, сдвиговые регистры будут выдавать на выход по одному биту – таблица 1.

Таблица 1.

Работа сдвиговых регистров

Начальное значение на входе регистра: 11001001

|

Номер такта |

Выход регистра |

|

1 |

1 |

|

2 |

0 |

|

3 |

0 |

|

4 |

1 |

|

5 |

0 |

|

6 |

0 |

|

7 |

1 |

|

8 |

1 |

Блок приема будет выдавать значения на блок промежуточного подсчета.

2.3 Блок промежуточного подсчета

Блок промежуточного подсчета – это одноразрядный сумматор. Данный блок обеспечивает сложение двух чисел побитово, организуя последовательное сложение. Каждый такт, данный функциональный блок выдает один бит результирующего значения, и этот бит подается на блок выдачи ответа. Также каждый такт формируется бит переноса, который подается на вход данного блока на следующей итерации сложения.

Данный функциональный блок состоит исключительно из ЛЭ и D-триггера. Триггер обеспечивает необходимую задержку для бита переноса для следующей итерации. Данный функциональный блок работает 8 тактов, так как разрядность исходных данных 8 бит.

2.4 Блок выдачи ответа

Блок выдачи ответа состоит из двух сдвиговых регистров, преобразующих последовательный код в параллельный. Один из регистров хранит выходное значение, которое будет формироваться каждый такт работы схемы, пока не окончится работа блока промежуточного подсчета. Второй регистр нужен для получения и хранения результирующего бита переноса.

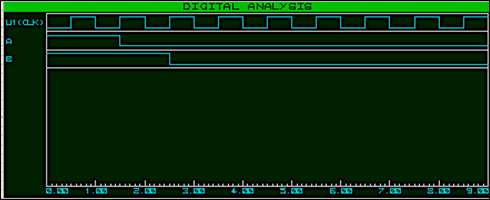

3 Построение временных диаграмм

Для начала промоделируем, как данные в регистры записываются на 1 такте, а далее, начиная со второго такта, потакнтно последовательно подаются на выход, начиная с младшего бита – рисунок 2.

Рисунок 2. Временная диаграмма сдвиговых регистров входа

Рисунок 3. Записанное число в регистры сдвига

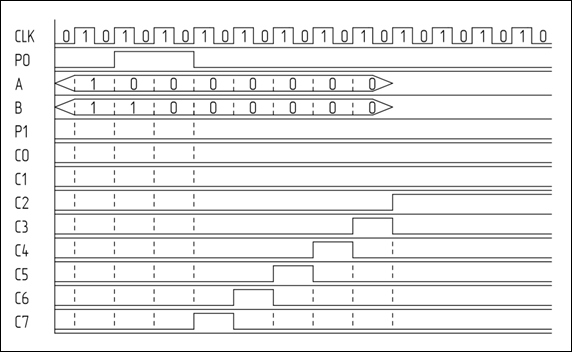

Результатом работы устройства будет выходное восьмиразрядное слово, полученное на 9 такте работы. На рисунке 4 представлена временная диаграмма выходов регистра ответа.

Рисунок 4. Временная диаграмма работы схемы

Итоговая временная диаграмма, объединяющая в себе входные и выходные результаты, а также промежуточные данные, представлена на рисунке 5 и также содержится в приложении Г.

Рисунок 5. Временная диаграмма

Рисунок 6. Пояснение сигналов к временной диаграмме

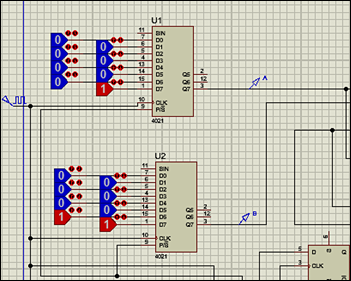

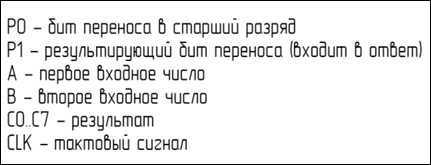

4 Синтез принципиальной схемы

Разработанная принципиальная схема восьмиразрядного сумматора последовательного действия представлена на рисунке 7 и в приложении В. Схема выполнена согласно ГОСТ 2.743-91 [2].

Рисунок 7. Принципиальная схема устройства

4.1 Выбор элементной базы

При выборе элементной базы прежде всего учтем быстродействие и потребляемую мощность элементов. В силу того, что по требованиям технического задания имеется ограничение на использование элементов только ТТЛ логики, элементная база должна состоять и серий МС, построенных на ТТЛ логике.

Цифровые интегральные МС на логике ТТЛ считаются менее перспективными, однако они имеют ряд преимуществ: высокое быстродействие, которое может достигать десятков мегагерц, хорошая помехоустойчивость, обширная номенклатура.

Отечественная промышленность производит широкий ассортимент логических МС, использующих структуры ТТЛ. На их основе выполнены такие распространенные серии, как К155, КР155. Рассмотрим данные, приведённые в таблице 3, – параметры отечественных серий ТТЛ-микросхем.

Серия К155 является самой полной серией микросхем ТТЛ. В неё входят около 100 микросхем различного назначения. В эту серию входят как все элементы базовой логики (И, ИЛИ, НЕ, И – НЕ, ИЛИ – НЕ) так и построенные на этих элементах более сложные узлы для выполнения логических операций: триггеры, регистры, счётчики, сумматоры.

Вся серия К155 является полным аналогом зарубежной серии SN74. Она была разработана в США ещё в 1965 году, но продолжает выпускаться до сих пор (аналогично и серии К155). На серии К155 процесс напыления в вакууме на монокристалл кремния структур ТТЛ весьма прост, что себестоимость микросхем ТТЛ по сравнению с другими микросхемами фантастически низкая.

Максимальная допустимая тактовая частота устройств серии К155 составляет 10МГц. Исходя из данных обстоятельств, отдадим предпочтение данной серии устройств.

На этапе синтеза функциональной схемы были определены основные устройства и ЛЭ, необходимые для построения схемы электрической принципиальной. Определимся с конкретными моделями устройств.

4.2 Выбор устройства хранения начальных данных

В качестве сдвиговых регистров, которые будут хранить исходные значения, используем элемент КР155ИР9. На рисунке 8 представлено УГО элемента.

Рисунок 8. УГО К155ИР9

Входы D1..D8 используются как шина данных для записи данных параллельного типа. Так же записывать данные можно не параллельно, а последовательно, для этого используется вход D0. Вход 2 (С) – тактовый вход. Инверсный вход 1 (L) используется как разрешающий вход для загрузки данных в регистр.

4.3 Выбор устройств подсчета тактов и формирования сигналов

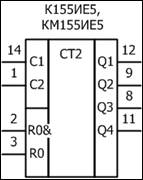

Для подсчета тактов требуются счетчик. Для данной схемы достаточно использовать 4 разрядный двоичный счетчик К155ИЕ5. УГО данного элемента представлено на рисунке 9.

Рисунок 9. УГО КР155ИЕ5

Микросхема КР155ИЕ5 - четырёхразрядный программируемый двоичный счетчик с возможностью запрещения счета. Счетчик КР155ИЕ5 с асинхронным сбросом и синхронной начальной загрузкой.

В таблице 2 представлены комбинации управляющих сигналов ИМС и соответствующие режимы работы.

Таблица 2.

Режимы работы К155ИЕ5

|

Вход |

Режим работы |

||||

|

Clock |

E |

EWR |

ECR |

R |

|

|

|

1 |

0 |

X |

X |

Предустановка |

|

|

1 |

1 |

0 |

X |

Нет счета |

|

|

1 |

1 |

X |

0 |

Нет счета |

|

|

1 |

1 |

1 |

1 |

Счет |

|

X |

0 |

X |

X |

X |

Сброс |

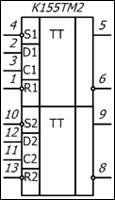

Для формирования правильных сигналов используются D-триггеры К155ТМ2. На рисунке 12 представлено УГО триггеров.

Рисунок 12. УГО К155ТМ2

Микросхема представляет из себя 2 D-триггера с динамическим управлением по входам синхронизации, имеющие входы асинхронной установки R и S .

При подаче на вход S логической 0 и на вход R – логической 1 триггер устанавливается в единичное состояние (Q = 1). При подаче на вход S логической «1» и на вход R – логического «0» триггер устанавливается в нулевое состояние. При S = R = 1 триггер работает как D-триггер, повторяя на выходе Q сигнал на входе D при воздействии положительного фронта на входе синхронизации.

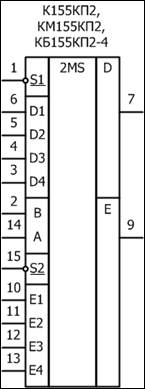

4.4 Выбор элемента, обеспечивающего выборку битов переноса

Для выбора используется микросхема КР155КП2. Данная ИМС представляет собой сдвоенный цифровой селектор-мультиплексор 4-1. На рисунке 13 представлено УГО ИМС.

Рисунок 13. УГО КР155КП2

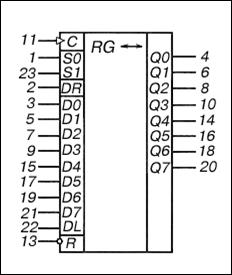

4.5 Выбор устройства хранения выходных данных

В качестве сдвиговых регистров, которые будут хранить выходные значения, используем элемент К155ИР13. На рисунке 14 представлено УГО элемента.

Рисунок 14. УГО К155ИР13

Вход используется как последовательный вход, а выходы Q0..Q7 – параллельный выход ИМС. C – тактовый вход. Для работы ИМС необходимо подать сигнал высокого уровня.

Именно сюда будет подан сигнал, не позволяющий дальнейшую запись данных в ИМС.

4.6 Выбор вспомогательных устройств

В качестве вспомогательных элементов выбираются:

- К155ЛП5 – 4 элемента «Исключающее ИЛИ»;

- КР155ЛИ1 – 4 элемента «И»;

- К155ЛЛ1 – 4 элемента «ИЛИ»;

- К155ЛН1 – 6 элементов «НЕ»;

- КМ155ЛА3 – 4 элемента «И-НЕ»;

- К155ЛЕ3 – 2 элемента «4 ИЛИ-НЕ».

4.7 Выбор конденсаторов, резисторов и кварцевого резонатора

Чтобы обеспечить стабильный режим работы устройства потребуется устранение помех по питанию. Для устранения скачков напряжения по нестабильности источника питания применим ряд конденсаторов. При этом необходимо обеспечить фильтрация и высокой частоты, и низкой. Для этого используется конденсатор MC0603F1 10 мкФ и 10 конденсаторов CC0603JRNPO 0,1мкФ.

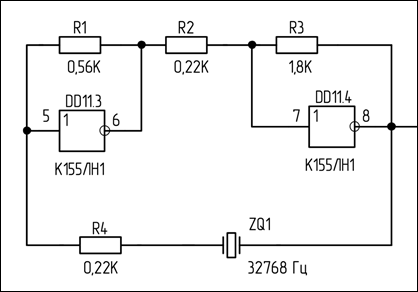

Для того, чтобы обеспечить схему стабильными тактовыми импульсами, необходимо собрать тактовый генератор с заданной частотой. На рисунке 15 представлена схема генератора.

Рисунок 15. Генератор тактовых импульсов

Для данной схемы используются резисторы C0603М различного номинала, а также кварцевый резонатор HCMOS/TTL с частотой 32768 Гц.

5 Расчет мощности устройства

Рассчитаем мощность, потребляемую сумматором последовательного действия. На все МС подано напряжение 5В. Суммарная мощность, потребляемая устройством, состоит из статической и динамической мощностей.

Рассчитаем статическую мощность, потребляемую спроектированным устройством, и приведем расчеты в таблице 3.

Таблица 3.

Расчет мощности, потребляемой в статическом режиме

|

ИМС |

Потребляемая мощность, Вт |

Количество |

Суммарная потребляемая мощность, Вт |

|

К155ИР9 |

0,21 |

2 |

0,42 |

|

К155ЛН1 |

0,0197 |

4 |

0,0788 |

|

К155ЛЛ1 |

0,051 |

2 |

0,102 |

|

КР155ЛИ1 |

0,035 |

6 |

0,21 |

|

К155ЛП5 |

0,066 |

3 |

0,198 |

|

КМ155ЛА3 |

0,019 |

1 |

0,019 |

|

К155ЛЕ3 |

0,046 |

1 |

0,046 |

|

К155ИР13 |

0,609 |

2 |

1,218 |

|

КР155КП2 |

0,315 |

1 |

0,315 |

|

К155ТМ2 |

0,078 |

1 |

0,078 |

|

КР155ИЕ5 |

0,265 |

1 |

0,265 |

ΣРсс=Icc∙10−3 ∙Ucc∙n, (1)

где потребляемый ток обозначается как Icc, напряжение питания обозначается как Ucc, а потребляемая мощность Рсс.

Таким образом, суммарная потребляемая мощность в статическом режиме равна 2,948 Вт.

Рассчитаем динамическую потребляемую мощность каждой микросхемы по формуле (1):

![]() , (2)

, (2)

где ![]() – входная емкость ИМС,

– входная емкость ИМС, ![]() – напряжение питания (5В),

– напряжение питания (5В), ![]() – емкость нагрузки,

– емкость нагрузки, ![]() и

и ![]() – входная и выходная частоты соответственно. Результаты представлены в таблице 4.

– входная и выходная частоты соответственно. Результаты представлены в таблице 4.

Таблица 4.

Расчет мощности, потребляемой в динамическом режиме

|

ИМС |

Потребляемая мощность, Вт |

Количество |

Суммарная потребляемая мощность, Вт |

|

К155ИР9 |

0,15 |

2 |

0,3 |

|

К155ЛН1 |

1,2 |

4 |

4,8 |

|

К155ЛЛ1 |

0,12 |

2 |

0,24 |

|

КР155ЛИ1 |

0,98 |

6 |

5,88 |

|

К155ЛП5 |

1,3 |

3 |

3,9 |

|

КМ155ЛА3 |

0,8 |

1 |

0,8 |

|

К155ЛЕ3 |

1,5 |

1 |

1,5 |

|

К155ИР13 |

2,2 |

2 |

4,4 |

|

КР155КП2 |

1,7 |

1 |

1,7 |

|

К155ТМ2 |

1,45 |

1 |

1,45 |

|

КР155ИЕ5 |

0,84 |

1 |

0,84 |

Таким образом, суммарная потребляемая мощность в динамическом режиме равна 25,81 Вт. Следовательно устройство потребляет 0,61 А, что примерно соответствует потребляемой мощности 2,948 Вт.

ЗАКЛЮЧЕНИЕ

В ходе выполнения проекта получены функциональное и принципиальное описание устройства, а также временные диаграммы симуляции его работы.

Устройство представляет собой восьмиразрядный сумматор последовательного действия. Сумматор полностью реализован на отечественных микросхемах логики TTL.

Начальная запись чисел производится в регистры, выходной ответ так же хранится в регистре.

Было произведено моделирование разработанного устройства в программе Proteus. По результатам моделирования было выяснено, что устройство работает корректно.

Устройство имеет следующие технические характеристики:

- Тип сумматора: последовательный

- Разрядность сумматора: 8бит

- Разрядность шины данных 16

- Логика элементов TTL

- Тактовая частота – 10 МГц.

- Мощность потребления – не более 3 Вт.

- Условия эксплуатации:

- температура окружающей среды 25-28 ℃

- относительная влажность воздуха до 80 %